日趋复杂的服务器设计

高速差分同轴线对板连接器系统,

最适合企业级计算设备的性能和机械需求。

现今的计算环境对于企业级设备提升其复杂程度的要求,达到了前所未有的高度。随着数据传输率的提高,受标准物料所限制的性能进一步加剧了复杂性的问题。

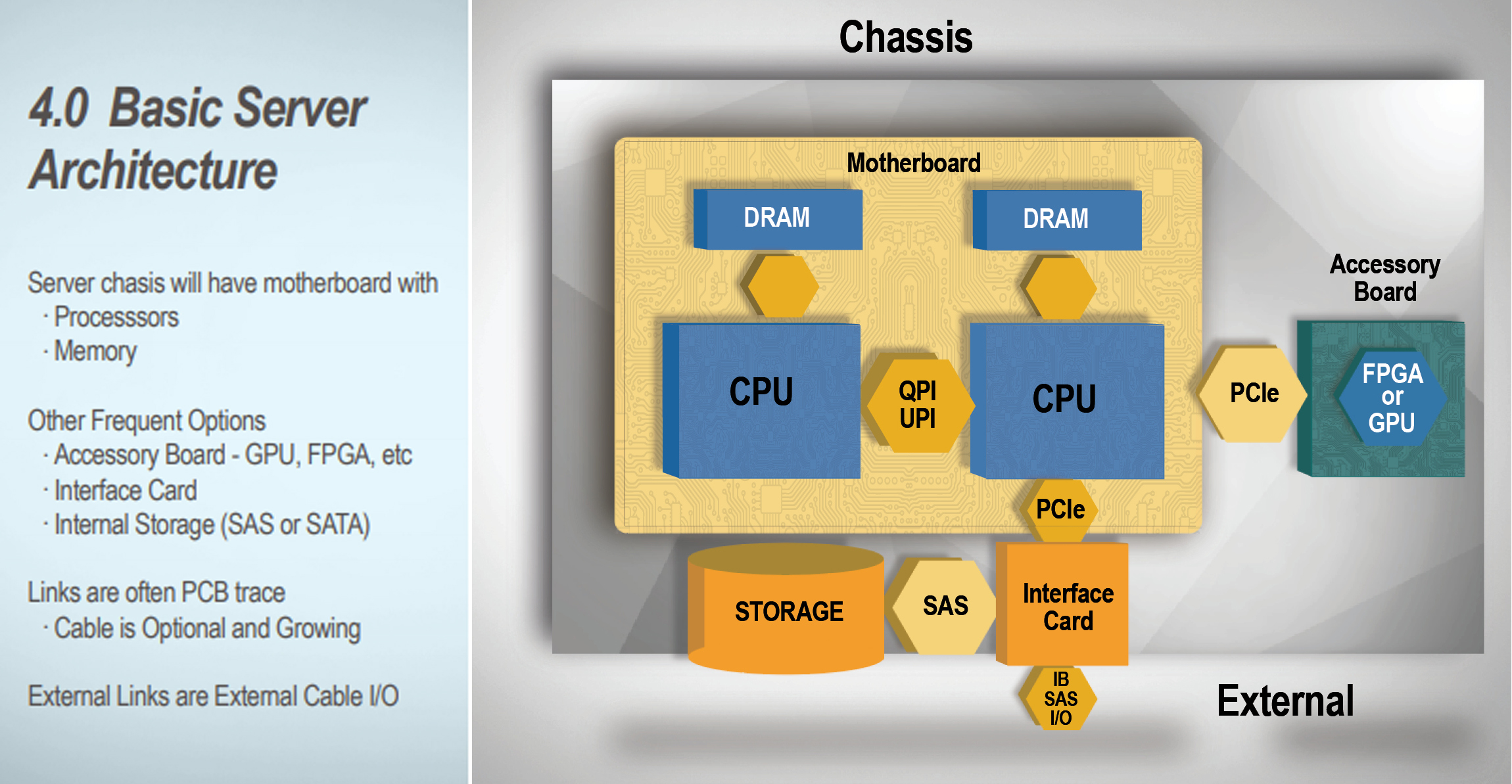

更快的数据传输率需要更快的上升时间,这亦导致更多高速讯号的损耗。虽然这个缺陷可以使用高性能的层压材料来进行弥补,但成效并不显著且成本大增。新款的处理器及主板会处理更多的输入/输出(I/O),使PCB的布线和布局密度有所增加。除PCI Express®外,板载储存应用可能会尝试布线至高速SAS。PCIe或SAS I/O信号可能因需要在服务器底盘内通过较长的距离而导致出现基于通道长度的损耗。采用PCIe重定时器是其中的一个选择,但随之而来的却是成本和复杂程度的增加。

由于重定时器会增加信号传输的延迟,因此并不能为高性能计算提供充分的解决方案。

这些相互抵触的需求使得PCB设计更加拥塞。增加层数也是一个选择,但却会为成本及性能带来冲击。由于减少走线宽度会导致在相同的数据传输率下进一步缩短信号到达的距离,因此并不是一个好的选择。而以增加走线宽度来作为补救的话则会增加PCB的拥塞问题,亦会发生和导致来自小间距的元器件的布线问题。

系统架构师应该做什么?

在最近几年可以看到高速内部电缆组件应用的增加趋势。此同时,由例如美国国家标准协会(ANSI)的T-10 SAS委员会就电缆对板系统亦设定了越来越多的工业标准。SAS 4能对应22.5Gbps,并具有能支持此规格的零件。

其他例如PCI Express(PCIe)具有非指定的组件 ,但通常是SAS型的组件。PCIe 3.0的规格为8GTps,但不能互连电缆组件。PCIe 4的规格为16GTps,并且是首个界定了内部电缆组件系统的PCIe标准。

PCIe被用作将处理器连接至SAS控制器和其他外围设备,例如一般用途图形处理器(GPU)。GPU最多可以占用PCIe的16条通道(32对再加上频率和接地),多数应用在关键任务和/或高性能设备上。现今企业级服务器已经可以将多个GPU合并到底盘内。由于PCB损耗和所有系统元器件之间需要一定的距离,将GPU组装到PCB是不切实际的。

双差分电缆组件可以填补此空隙,亦为GPU配置提供了更多机械选项。

由于系统的电源消耗量和散热都会随着处理器和GPU上升,因此配置是一个重要的考虑因素。气流亦是关键所在,不能有所阻挡。使用电缆组件的挑战,就是在于如何既能满足机械和连接上的要求,又能避免产生气流的阻挡。

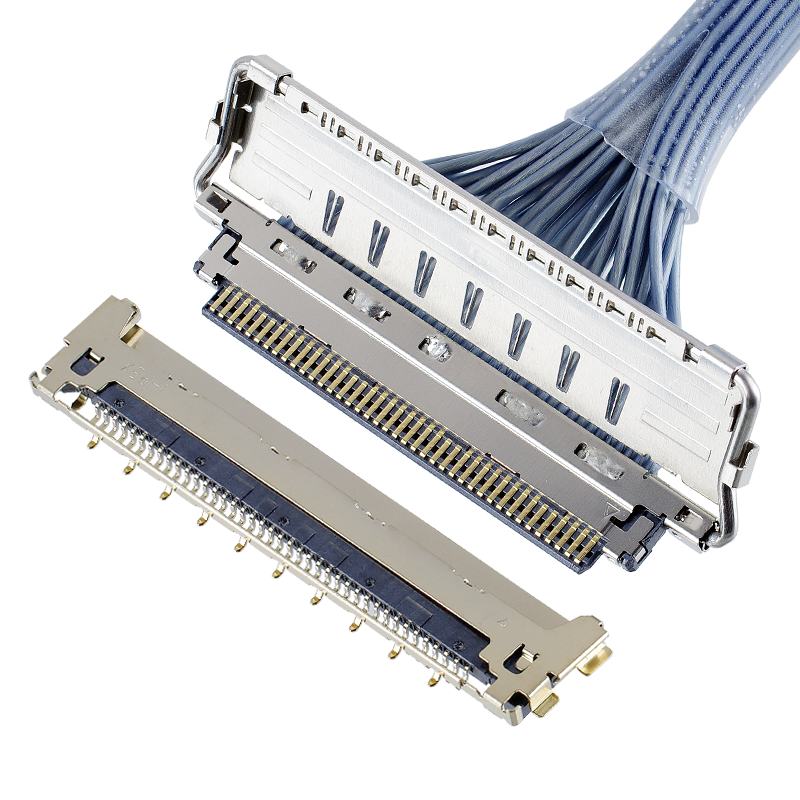

因此,考虑电缆组件附近的机械标准是十分重要的。低高度、低损耗、密度和灵活性都是希望能被满足的功能。部分电缆组件需要复杂地布线通过某个系统,要求更大的折弯半径,占用更多的空间。部分电缆组件虽然是低高度,但却需要精细的折迭。大部分电缆组件不具有360度的灵活性,或为了增加电缆的刚性而采用固体的导体。

有360度的EMI屏蔽,提供板上配置的

最大灵活性。

在手提电脑和其他设备上使用极细同轴组件已经有很长的历史,在采用USB-C的情况下,传输速度更可高达20Gbps。同轴线既能通过差分驱动,又能将对讯号完整性功能的影响减至最低。极细同轴组件的优异性与双轴组件相近,但由于极细同轴组件多数采用绞线,因此大大增加了灵活性。

此外还需要考虑的便是极细同轴组件成本下降这个由移动计算市场的规模经济所带来的最大好处。

极细同轴组件的性能因直接端接而得以提升。这样能消除PCB损耗的情况,并能减少与PCB关连的额外端接。这些多余的不连续性与反射源都会降低信号完整性。

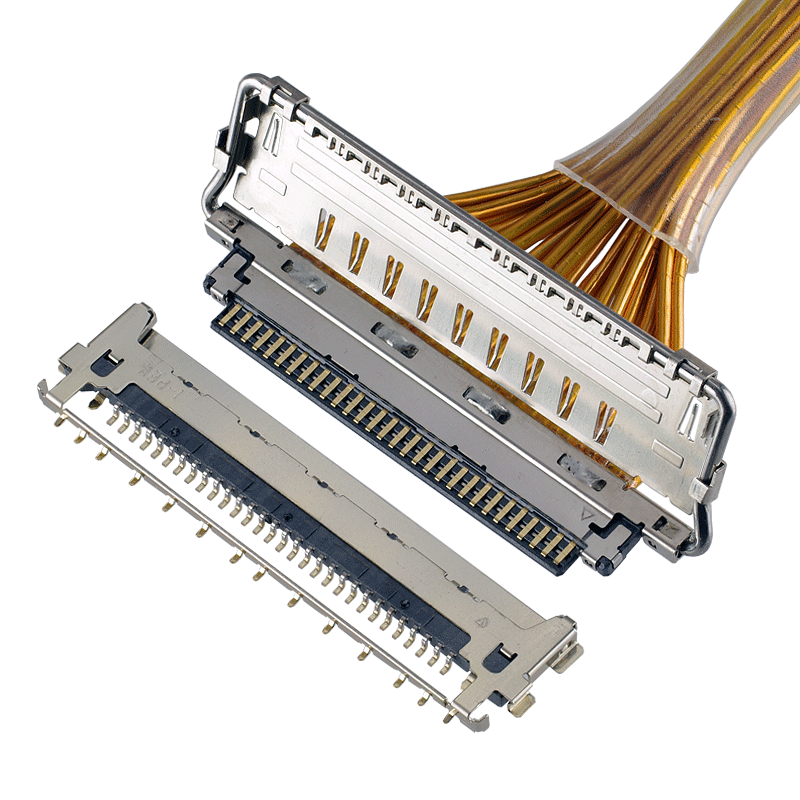

电缆组件的电线配置备有平面式、绑定式或混合式的构造。连接器提供了极低高度的端接,让高度低于2mm的全屏蔽的直角发射成为可能,并提供了带锁存的垂直屏蔽端接与其他功能。

应用的可能性广泛,包括在横跨板上的直接跳线器组件、以及可以在PCB和底盘之间的主板之下布线或在零件和底盘侧壁之间布线的低高度的组件。亦提供抗高温的电缆,以助解决所有在应用时有关温度的问题,使连接器可以配置在处理器的附近位置。

若需要更多信息,以及I-PEX连接器如何选型以符合您的系统需要,请联系您的I-PEX Connectors业务代表或“联系我们”进行咨询。