ウエハー製品 (KRYSTAL® Wafer)

KRYSTAL® Wafer

独自開発のZrO2 Buffer(下地層)を使用することにより、上に成膜するPZT薄膜を単結晶化し高性能化することができる優れた圧電MEMS用ウエハーです。

標準PZT薄膜 KRYSTAL® Wafer

- 標準ウエハーサイズ: 4インチ、6インチ、8インチ

上部電極付き単結晶PZTウエハー

単結晶PZTウエハー

下部電極SRO/Ptウエハー(SRO/Pt/ZrO2)

下部電極Ptウエハー(Pt/ZrO2)

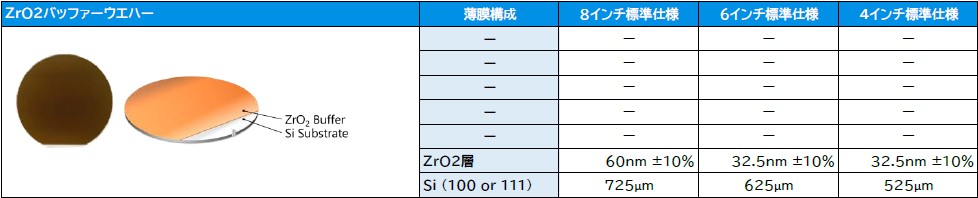

ZrO2バッファーウエハー(ZrO2)

Si基板への標準成膜以外にカスタム成膜対応として、ご希望膜厚での成膜やSOI基板への成膜、お客様からご支給頂いた基板への成膜サービスも行っております。

新規開発技術

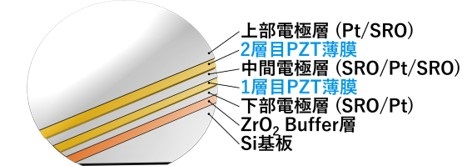

RYSTAL® Wafer の優れた単結晶成膜技術を応用し、単結晶薄膜PZTを積層成膜。 圧電特性が向上し、高出力・高精度なアクチュエーター駆動を実現可能。

RYSTAL® Wafer の優れた単結晶成膜技術を応用し、単結晶薄膜PZTを積層成膜。 圧電特性が向上し、高出力・高精度なアクチュエーター駆動を実現可能。

更に詳しく

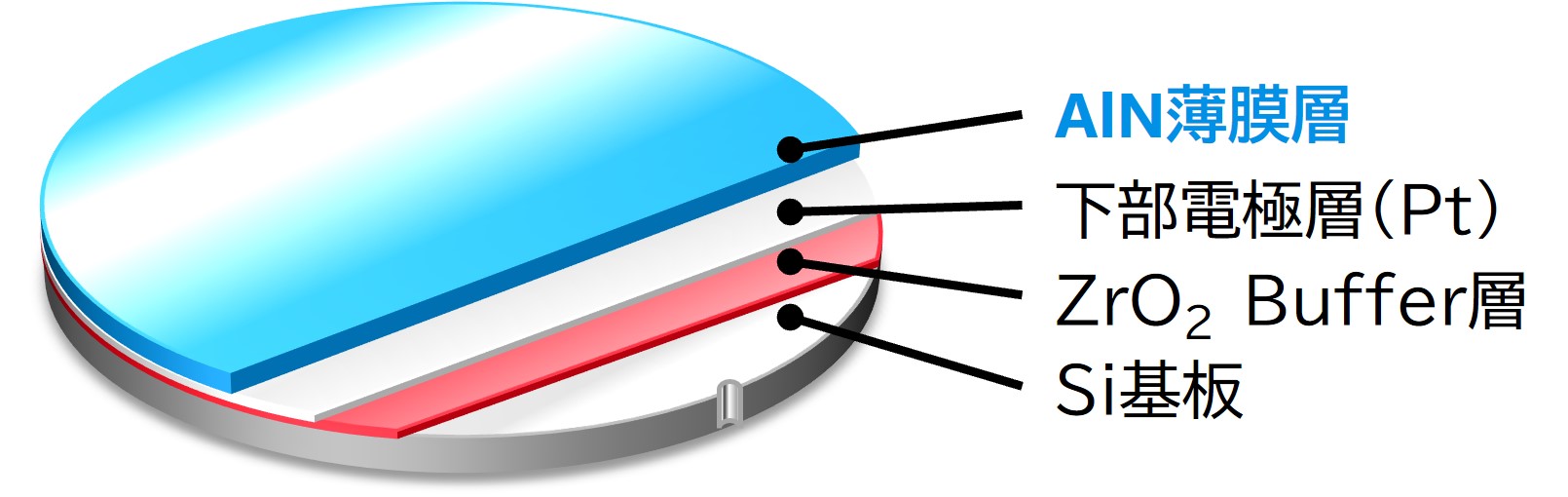

独自ZrO2バッファー層技術により、AlNエピタキシャル成長 on Siを実現。

独自ZrO2バッファー層技術により、AlNエピタキシャル成長 on Siを実現。

更に詳しく