# KRYSTAL Wafer

## 標準品

### KRYSTAL® Wafer

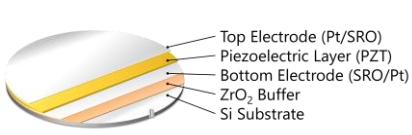

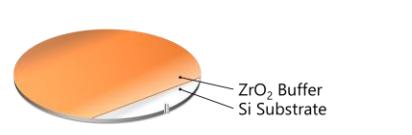

独自開発のZrO<sub>2</sub> Buffer(下地層)を使用することにより、上に成膜するPZT薄膜を単結晶化し高性能化することができる優れた圧電MEMS用ウエハーです。

一般的な圧電薄膜と比較してKRYSTAL® Wafer単結晶圧電薄膜は、電気的、機械的に優れた特性を発揮します。

標準品の仕様は下記の通り：

| 上部電極付きPZTウエハー(アクチュエータータイプ)                                                        | 薄膜構成               | 8インチ標準仕様    | 6インチ標準仕様    | 4インチ標準仕様    |

|-----------------------------------------------------------------------------------|--------------------|-------------|-------------|-------------|

|  | 上部Pt層              | 100nm (目標値) | 100nm (目標値) | 100nm (目標値) |

|  | 上部SRO層             | 10nm (目標値)  | 10nm (目標値)  | 10nm (目標値)  |

|                                                                                   | PZT層               | 2000nm ±10% | 2000nm ±10% | 2000nm ±10% |

|                                                                                   | 下部SRO層             | 40nm ±10%   | 32.5nm ±10% | 32.5nm ±10% |

|                                                                                   | 下部Pt層              | 150nm ±10%  | 104nm ±10%  | 104nm ±10%  |

|                                                                                   | ZrO <sub>2</sub> 層 | 60nm ±10%   | 7nm ±15%    | 7nm ±15%    |

|                                                                                   | Si (100 or 111)    | 725μm       | 625μm       | 525μm       |

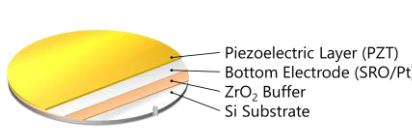

| PZTウエハー(アクチュエータータイプ)                                                              | 薄膜構成               | 8インチ標準仕様    | 6インチ標準仕様    | 4インチ標準仕様    |

|-----------------------------------------------------------------------------------|--------------------|-------------|-------------|-------------|

|  | —                  | —           | —           | —           |

|  | —                  | —           | —           | —           |

|                                                                                   | PZT層               | 2000nm ±10% | 2000nm ±10% | 2000nm ±10% |

|                                                                                   | 下部SRO層             | 40nm ±10%   | 32.5nm ±10% | 32.5nm ±10% |

|                                                                                   | 下部Pt層              | 150nm ±10%  | 104nm ±10%  | 104nm ±10%  |

|                                                                                   | ZrO <sub>2</sub> 層 | 60nm ±10%   | 7nm ±15%    | 7nm ±15%    |

|                                                                                   | Si (100 or 111)    | 725μm       | 625μm       | 525μm       |

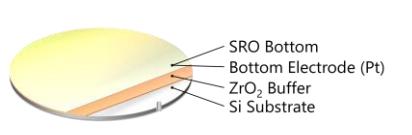

| 下部電極SRO/Ptウエハー                                                                      | 薄膜構成               | 8インチ標準仕様   | 6インチ標準仕様    | 4インチ標準仕様    |

|-------------------------------------------------------------------------------------|--------------------|------------|-------------|-------------|

|  | —                  | —          | —           | —           |

|  | —                  | —          | —           | —           |

|                                                                                     | —                  | —          | —           | —           |

|                                                                                     | 下部SRO層             | 40nm ±10%  | 32.5nm ±10% | 32.5nm ±10% |

|                                                                                     | 下部Pt層              | 150nm ±10% | 104nm ±10%  | 104nm ±10%  |

|                                                                                     | ZrO <sub>2</sub> 層 | 60nm ±10%  | 7nm ±15%    | 7nm ±15%    |

|                                                                                     | Si (100 or 111)    | 725μm      | 625μm       | 525μm       |

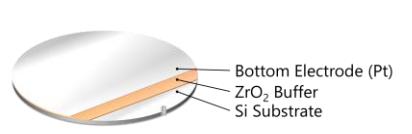

| 下部電極Ptウエハー                                                                          | 薄膜構成               | 8インチ標準仕様   | 6インチ標準仕様   | 4インチ標準仕様   |

|-------------------------------------------------------------------------------------|--------------------|------------|------------|------------|

|  | —                  | —          | —          | —          |

|  | —                  | —          | —          | —          |

|                                                                                     | —                  | —          | —          | —          |

|                                                                                     | —                  | —          | —          | —          |

|                                                                                     | 下部Pt層              | 150nm ±10% | 104nm ±10% | 104nm ±10% |

|                                                                                     | ZrO <sub>2</sub> 層 | 60nm ±10%  | 7nm ±15%   | 7nm ±15%   |

|                                                                                     | Si (100 or 111)    | 725μm      | 625μm      | 525μm      |

| ZrO <sub>2</sub> バッファーウエハー                                                          | 薄膜構成               | 8インチ標準仕様  | 6インチ標準仕様 | 4インチ標準仕様 |

|-------------------------------------------------------------------------------------|--------------------|-----------|----------|----------|

|  | —                  | —         | —        | —        |

|  | —                  | —         | —        | —        |

|                                                                                     | —                  | —         | —        | —        |

|                                                                                     | —                  | —         | —        | —        |

|                                                                                     | —                  | —         | —        | —        |

|                                                                                     | ZrO <sub>2</sub> 層 | 60nm ±10% | 7nm ±15% | 7nm ±15% |

|                                                                                     | Si (100 or 111)    | 725μm     | 625μm    | 525μm    |

ご不明な点がございましたら、営業担当者にご連絡ください。

連絡先:I-PEX Piezo Solutions 株式会社 横浜オフィス(営業所)

〒222-0033 横浜市港北区新横浜二丁目3 番地12 新横浜スクエアビル 11階 (TEL: 045-472-7111)

# KRYSTAL Wafer

## 仕様条件説明書

発行日：2026年1月20日

特段の指定がない場合は、「仕様条件説明書」に記載の方法に従って対応致します。

### ■ベアSi 基板について

IPS手配の標準ベアSi基板はJEITA 規格、オリフラ方位110 を標準として使用します。

### ■カスタム成膜サービスについて

Si基板への標準成膜以外にもカスタム成膜対応として、ご希望膜厚での成膜やご支給基板への成膜、またSOI基板への成膜も行っております。

※カスタム成膜対応のご注意点：

基板成膜面の状態は成膜品質に影響するため、汚れやキズ、有機汚染等の無いクリーンな基板のご提供をお願いしております。

弊社での基板受入検査にて成膜面に汚染の懸念が確認された場合、成膜作業前にお客様のご負担にてRCA洗浄(または、状態によってはスクラブ洗浄+RCA洗浄)をお願いする場合があります。

また弊社での基板受入検査ではUVライトを用いて基板の状態を確認しておりますが、有機汚染の検出が困難な場合があります。

そのため、成膜後の外観検査や結晶性試験において有機汚染が原因と疑われる品質異常が検出された場合でも、お客様へご報告のうえ、納品をさせていただいているので予めご了承ください。

また、新規仕様のSOI基板への成膜をご希望の場合は、納入する成膜ウエハ一枚数とは別に、最初の成膜条件設定用として余分に1枚ご準備いただく必要があります。

SOI基板の仕様によっては、条件設定に複数枚が必要となる場合がございます。その際は、1枚目での成膜結果を確認したうえで、今後の進め方についてご相談させていただきます。

### ■基板特性と検査方法について

| 項目             | 仕様                                                                | 検査方法                                  |

|----------------|-------------------------------------------------------------------|---------------------------------------|

| 単結晶比率<br>(配向率) | 96 % 以上<br>*単結晶比率計算式<br>PZT(001)Int./ (PZT(001)Int.+PZT(110)Int.) | 基板内3点(*1)を全自动多目的水平型X線回析装置(XRD)にて結晶性評価 |

| 膜厚             | 別紙Spec. Sheetに記載の通り                                               | 基板内3点(*1)を蛍光X線分析装置(XRF)にて測定           |

| 外観             | 100 μm以上のパーティクルなきこと                                               | 目視及びマイクロスコープによる外観検査                   |

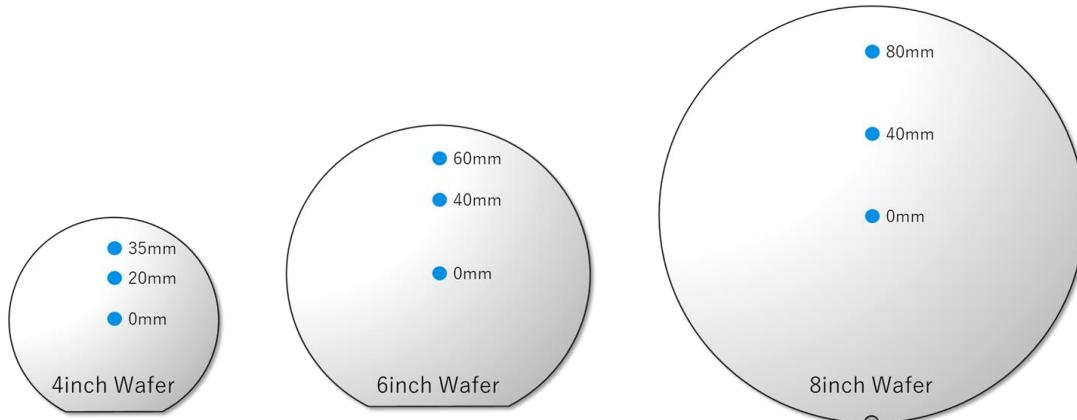

(\*1) 基板内3点測定箇所例

基板センターから、R寸法にて記載

### ■基板の取扱い方法について

弊社製造工程内の標準基板取扱い方法では、基板搬送時に基板裏面を真空ピンセットで吸着して取扱いいたします。

その他ご不明な点がございましたら、営業担当者にご連絡ください。

連絡先:I-PEX Piezo Solutions 株式会社 横浜オフィス(営業所)

〒222-0033 横浜市港北区新横浜二丁目3 番地12 新横浜スクエアビル 11階 (TEL: 045-472-7111)